**INSIDE**

News Review, Features, News Analysis, Profiles, Research Review and much more...

# It's time to commercialise the GaN IC

Power ICs combine several power functions in a GaN chip are set to play a major role in worldwide electrification

# There is still life in the silicon IGBT

With the recent Tesla announcement, is SiC the way forward for EV power electronics?

# Controlling threshold voltage instabilities in SiC MOSFETs

System designers can benefit from test and stress procedures for SiC MOSFETs that determine their worstcase threshold voltage variations

# Global mega trends require best performance III-V materials

## **AIX 2800G4-TM**

- 3D sensing

- Augmented reality

- Autonomous driving

- Cloud computing

- Internet of things

- Next generation displays

Discover the MOCVD tool of record for AsP-based applications

Made in

Germany

info@aixtron.com www.aixtron.com

# **VIEWPOINT**

By Christine Evans-Pughe, Acting Editor

# There's more to power electronics than new materials

WIDE bandgap power semiconductor devices based on silicon carbide (SiC) and Gallium Nitride (GaN) are evolving fast and playing a greater role in many applications. But there is far more to power electronics than new materials.

At the device level, architecture matters. And of course, there's the wider impact of big global trends such as the growth in renewable energy generation.

In this edition of Power Electronics World, we look at the latest development in power GaN and new test procedures for SiC; we revisit the silicon IGBT; and discover how architectures can revolutionise power devices. As power grids shift from one-directional power flow to integrating renewable energy resources, we also explore the benefits of virtualisation.

In March, Tesla announced that it will use 75 percent less SiC in a new EV powertrain, sending a shockwave through an industry investing \$billions in SiC fabs. But as our news analysis explains, there is plenty of life left in silicon IGBTs.

SiC is the long-term future. As well as new fabs coming on stream, other developments are continuing apace including, as Infineon outlines in its article, new test and stress procedures for SiC MOSFETs.

We have several interesting GaN articles. Innoscience looks at how bidirectional GaN switches are disrupting power management, while Wise Integration details how highly integrated GaN chips are set to play a greater role in power electronics. Jim Witham, CEO of GaN Systems, explains why surging sales EVs, data centres and industrial motors, have brought GaN devices to a key inflection point.

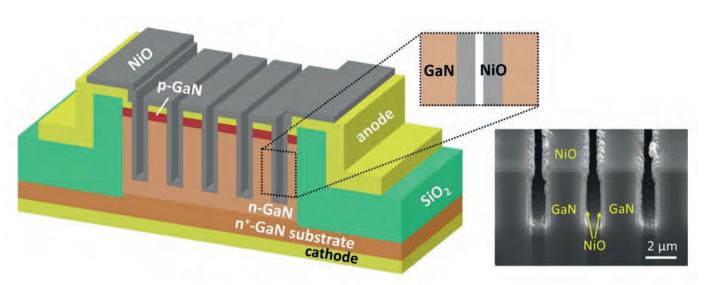

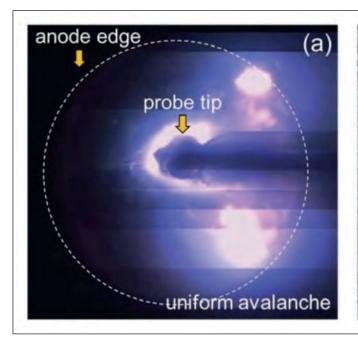

Back in the lab, researchers at Stanford University describe how a multi-faceted endeavour, starting

with material growth and extending all the way to circuit-level investigation, can ensure uniform, robust avalanche in GaN vertical power diodes.

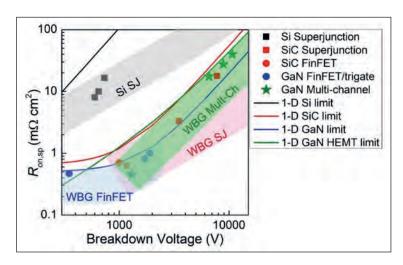

Of course, new materials are only part of the story of innovation. Yuhao Zhang from Virginia Tech reminds us that architectures matter, with the likes of superjunctions, multiple channels and multiple gates offering the opportunity to revolutionise power devices.

And finally, there's the big picture. Power grids must evolve to integrate renewable energy resources. In a fascinating overview, ABB explains how virtualisation of protection and control forms a key part of this journey, offering new possibilities to optimise the supply of renewable generation and achieve flexibility and scale.

Power grids are undergoing a period of radical change. Henry Niveri, product manager at ABB, explores the transition to virtualised protection and control in the age of renewables.

power grid

### 18 Bidirectional GaN switches are disrupting power management

Bidirectional voltage blocking and current conduction is an important function in overvoltage protection.

#### 22 There is still life in the silicon IGBT

Tesla's recent announcement that it will use 75 percent less silicon carbide (SiC) in a new powertrain for lower cost EVs sent a small shock-wave through the industry.

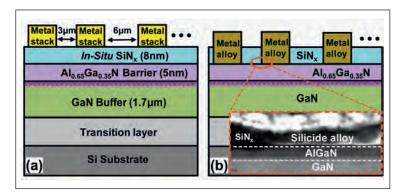

### 24 Targeting the C-band with ultra-high-voltage HEMTs

GaN HEMTs with a minimal output capacitance and terminated harmonics deliver record-breaking powers and efficiencies.

### 30 Controlling threshold voltage instabilities in SiC MOSFETs

System designers can now benefit from new test and stress procedures for SiC MOSFETs that realistically determine their worst-case threshold voltage variations.

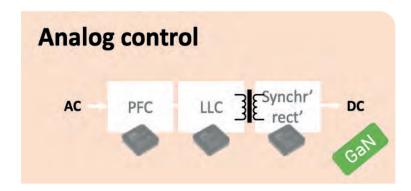

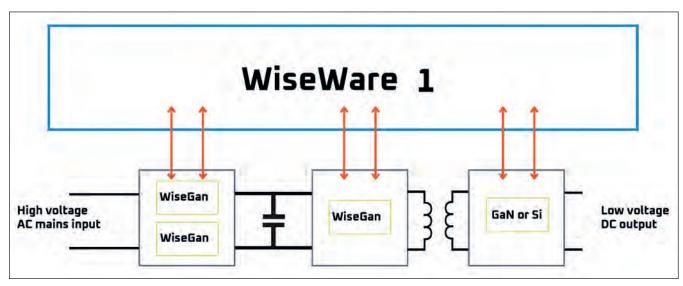

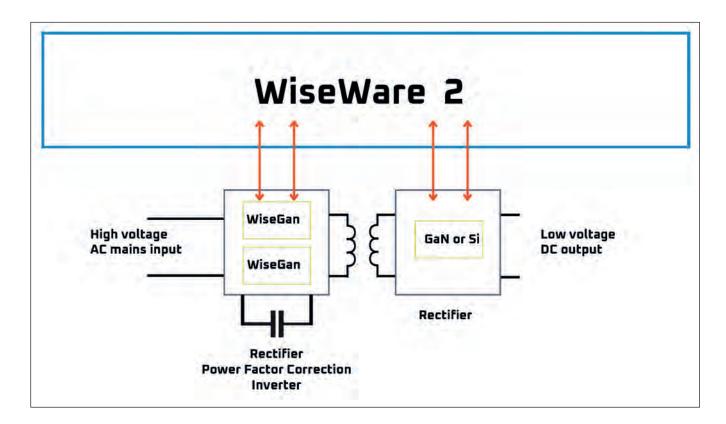

### 36 Now's the time to commercialise the GaN IC

Power ICs that combine several power electronics functions in a single GaN chip are set to play a major role in worldwide electrification.

#### 42 Multi-dimensional power devices

Advancing power electronics is not all about new materials. Architectures really matter, with the likes of superjunctions, multiple channels and multiple gates offering the opportunity to revolutionise power devices.

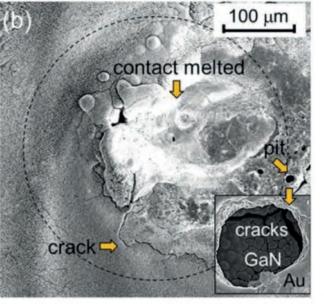

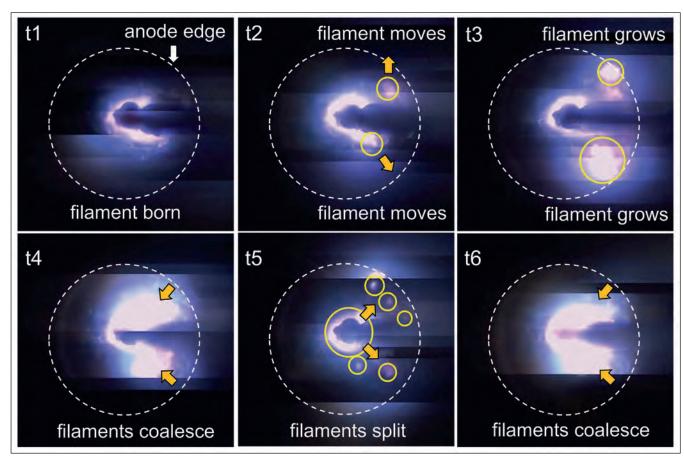

### 46 GaN diodes with uniform, robust avalanche

A multi-faceted endeavour, starting from material growth and extending all the way to circuit-level investigations, ensures uniform, robust avalanche in GaN vertical power diodes.

#### RESEARCH REVIEW

- **52** SiN trims the contact resistance of high-speed HEMTs

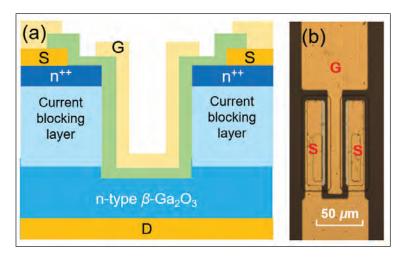

- 53 Enhancing the credentials of  $Ga_2O_3$  with a novel MOSFET

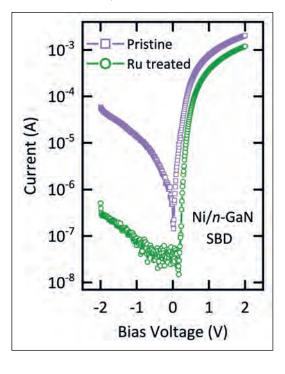

- 54 Passivating GaN with ruthenium

#### **NEWS**

- **06** EU PowerizeD project aims to transform power electronics

- 07 Gridspertise and ST extend 20-year collaboration

- **08** Infineon QDPAK and DDPAK registered as JEDEC standard

- **09** US DOE announces \$48M grid project

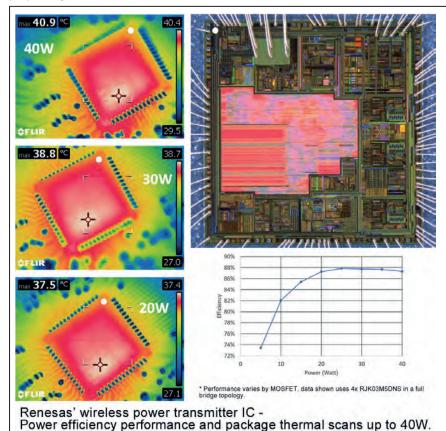

- 10 Renesas presents wireless power transmitter update

- 11 Mitsubishi acquires Swedish DC circuit breaker firm

- 12 Microchip invests to expand SiC capacity

#### Acting Editor

Christine Evans-Pughe christine.evans-pughe@angelbc.com

#### Contributing Technical Editor Richard Stevenson

richard.stevenson@angelbc.com +44 (0)1923 690215

#### Sales & Marketing Manager Shehzad Munshi

shehzad.munshi@angelbc.com +44 (0)1923 690215

#### Senior Event and Media Executive for Power Electronics International

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

#### **Design & Production Manager** Mitch Gaynor

mitch.gaynor@angelbc.com +44 (0)1923 690214

#### Publisher

Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price \$4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2023. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.® Copyright 2023.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com W: angelbc.com

#### EU PowerizeD project aims to transform power electronics

Multi million euro European research initiative will involve 39 companies and 23 research institutions

A NEW RESEARCH initiative called PowerizeD, involving 39 companies and 23 research institutions, aims to transform power electronics in Europe.

Coordinated by Infineon Technologies AG, PowerizeD aims to increase the degree of mechanical and electrical integration of control, driver and switching functionalities in components and to advance the integrated optimisation of all power switch functions, independent of the semiconductor material used.

New switching topologies and advanced control strategies involving the application of Artificial Intelligence are expected to improve efficient, robust and reliable operations even further.

The immediate project objectives include: reduction of power loss in power conversion by 25 percent; extension of the service lives of devices and systems by 30 percent;; reduction of chip size by at least 10 percent; and shortening development times by a challenging 50 percent.

The project partners are focusing on applications from the fields energy and mobility. 17 demonstrator paths are concerned among other things with improvement of drives for the rail industry, charging systems for the automotive industry, liquid batteries for the energy industry as well as drives for the manufacturing industries. The research partners will take an interdisciplinary approach with topics

including modeling and Digital Twin, Federated Learning as well as reliability and sustainability.

"We have to make highly efficient use of energy if we are to achieve net-zero climate protection goals. Digitalisation can help here as a highly decisive lever for more energy efficiency," says Constanze Hufenbecher, Infineon chief digital transformation officer.

"Power electronics is key to the energy transformation and is used anywhere and everywhere that electricity is generated, transferred and used efficiently," says Dr. Rutger Wijburg, COO at Infineon. "The broad spectrum of power electronics applications makes it very important that we collaborate with partners across the boundaries of corporate entities and organisations to

jointly advance Europe as innovation engine."

The European Union is funding PowerizeD with approximately €18 million as part of the joint program for digital key technologies (Key Digital Technologies Joint Undertaking, KDT JU) in its Digital Agenda. The amount will be matched by funding from the national governments of the respective countries involved.

The subsidies from Germany are being provided by the German Federal Ministry of Education and Research. A summary of all the project partners and supporting organisations is available on the project web site. The project will have a three-year duration and is expected to end in December 2025.

The broad spectrum of power electronics applications makes it very important that we collaborate with partners across the boundaries of corporate entities and organisations to jointly advance Europe as innovation engine

#### Gridspertise and ST extend 20-year collaboration

Companies to add features to smart-meter customers in the US and other geographies

GRIDSPERTISE and STMicroelectronics (ST) have entered a new phase in their 20 year smart-meter collaboration.

Over 65 million Gridspertise smart meters deployed in Spain, Eastern Europe, and Latin America already use ST's power-line communication (PLC) technologies. And ST's latest PLC system-on-chip has been integrated in Gridspertise smart meters for Italy to enable a near real-time cybersecure communication channel for in-home devices; the so-called Chain 2 technology.

Now, Gridspertise and ST are working together to extend Chain 2 to new metering solutions in the Gridspertise portfolio, making it suitable for the US and other geographies.

Chain 2 technology aims to improve customer awareness of the energy consumed and self-produced. For example, it enables the smart meter to collect real-time data on home appliances' consumption, that can be used, for example, to modulate the charging power of an EV charger according to the available capacity and other demands for power in the house.

Gridspertise and ST are collaborating in other areas too. Beyond working on ANSI C communication standard for the US market, the companies are cooperating for the adoption of the latest DLMS-certified standards into Gridspertise smart meters, to further enhance interoperability and interchangeability between devices and systems.

"Working together with other key industry leaders is fundamental to accelerating grid digitalisation and to promoting an active role for end users in the energy transition," said Gianni Ceneri, CTO. "We are pleased to strengthen our strategic collaboration with STMicroelectronics

leveraging shared best practices for the development of innovative solutions to serve an ever-increasing number of markets and bring benefits to new customers, starting from the US where Gridspertise is enhancing its activities through its North American platform to better support power grid operators and utilities in the region."

"As Gridspertise accelerates the growth of its business, ST continues to develop and contribute our unique system know-how, dedicated support, and ready-to-use solutions based on our advanced semiconductor integration capabilities," added Domenico Arrigo, general manager of STMicroelectronics's Industrial and Power Conversion Division in the Analog, MEMS & Sensors Group.

"We are maintaining and enhancing our connection as a key technology provider for Gridspertise solutions and services, and with them delivering smart and sustainable grids that are robust, secure, resilient, and reliable."

Beyond working on ANSI C communication standard for the US market, the companies are cooperating for the adoption of the latest DLMS-certified standards into Gridspertise smart meters, to further enhance interoperability and interchangeability between devices and systems

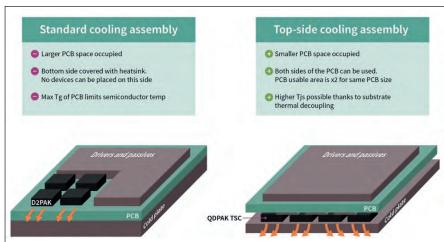

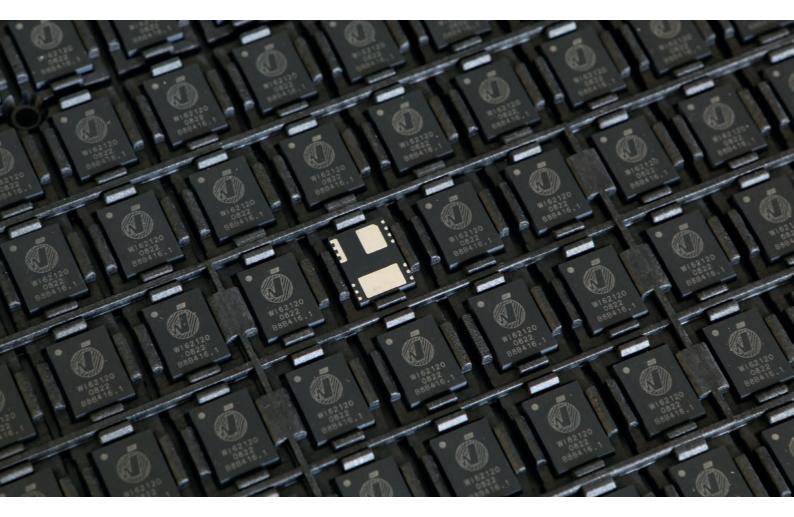

#### Infineon QDPAK and DDPAK registered as JEDEC standard

New top-side cooling packages for high-voltage MOSFETs registered as JEDEC standard for high-power applications

INFINEON TECHNOLOGIES has successfully registered its QDPAK and DDPAK top-side cooling (TSC) packages for high-voltage MOSFETs as a JEDEC standard. This registration further solidifies Infineon's goal to help establish a broad adoption of TSC in new designs with one standard package design and footprint.

"As a solutions provider, Infineon continues to influence the semiconductor industry through innovative packaging technologies and manufacturing processes," said Ralf Otremba, lead principal engineer for High Voltage Packaging, Infineon.

"Our advanced top-side cooled packages bring significant advantages to the device and system levels to fulfill the challenging demands of cutting-edge high-power designs. Package outline standardisation will help ease one of the main design concerns of OEMs for high-voltage applications by securing pin-to-pin compatibility across vendors."

JEDEC has been widely accepting semiconductor packages such as the TO220 and TO247 through-hole devices (THD) – devices that have been prominently used over the past decades and are still an option in new onboard charger (OBC) designs, high voltage (HV) and low voltage (LV) DC-DC converters.

The registration of QDPAK and DDPAK surface-mounted (SMD) TSC package designs signals a new era for package outlines, says Infineon, ushering a wide market adoption of the TSC technology as a replacement for TO247 and TO220, respectively. With the benefits of this technology, this new JEDEC package family registration, according to the MO-354 standard, serves as a key enabler for the transition of high-voltage industrial and automotive applications to top-side cooled designs in next-generation platforms.

To facilitate design transition for customers from the TO220 and TO247 THD devices, Infineon has designed QDPAK and DDPAK SMD devices to deliver equivalent thermal capabilities with improved electrical performance. Based on a standard height of 2.3 mm for QDPAK and DDPAK SMD TSC package for HV and LV devices, developers are now able to design complete applications such as OBC and DC-DC conversion with all SMD TSC devices measuring the same height. Compared to existing solutions

Additionally, TSC packaging offers up to 35 percent lower thermal resistance than standard bottom-side cooling (BSC)

that require a 3D cooling system, this facilitates designs and reduces system cost for cooling.

Additionally, TSC packaging offers up to 35 percent lower thermal resistance than standard bottom-side cooling (BSC). By enabling the use of both PCB sides, TSC packages offer better board space utilisation and at least two times more power density.

The thermal management of the packages is also improved by thermal decoupling from the substrate since the thermal resistance of the leads is much higher compared to the exposed package top side.

Because of the improved thermal performance, stacking different boards is not necessary. Rather than combining both FR4 and IMS, a single FR4 is enough for all components and also requires fewer connectors. These features deliver an overall bill of materials (BOM), which ultimately reduces overall system cost.

TSC technology is also said to offer an optimised power loop design for increased reliability. This is possible by the placement of the drivers, which can be placed very close to the power switch. The low stray inductance of the driver switch loop, reduces the loop parasitics and leads to less ringing on the gate, higher performance and a smaller risk of failures.

#### US DOE announces \$48 million grid project

ULTRAFAST project will advance performance limits of silicon, wide bandgap, and ultrawide bandgap semiconductors to improve their actuation methods

THE US Department of Energy (DOE) has announced \$48 million in funding to support a new program focused on developing power grid technologies that improve control and protection of the US domestic power grid.

The goal of ULTRAFAST (Unlocking Lasting Transformative Resiliency Advances by Faster Actuation of Power Semiconductor technologies) is to advance the performance limits of silicon, wide bandgap (WBG), and ultrawide bandgap (UWBG) semiconductor devices that will enable faster switching and/or triggering at higher current and voltage levels for improved control and protection of the grid.

Unforeseen power grid outages are estimated to cost the US economy \$150 billion annually. The DOE says that modernising the US grid infrastructure with improved efficiency and resilience against extreme weather events is critical to ensuring that clean energy and transportation options can reach communities across the country. Grid modernisation will also support President Biden's goals to accelerate

the deployment of renewables, boost the nation's energy independence, and achieve 100 percent clean electricity by 2035

ULTRAFAST will fund projects that aim to enable utilities to more effectively control grid power flow to avoid disturbances, and quickly isolate and route around disruptions.

Managed by DOE's Advanced Research Projects Agency-Energy (ARPA-E), the ULTRAFAST's categories include:

- Device and/or module technologies targeting protection functions at high current and voltage levels by achieving very fast by-pass, shunt, or interrupt capability at as low level of integration as possible with nanosecond-level reaction time (and corresponding slew rates).

- High switching frequency devices and/or modules which enable efficient, high-power, high-speed power electronics converters.

- Complementary technologies such as wireless sensing of voltage and current, high-density packaging

with the integrated wireless actuators and device/module-level protection, power cell-level capacitors and inductors, and thermal management strategies to support (1) and (2).

ARPA-E first held a workshop on this topic last year. Workshop participants provided expert inputs on the technical aspects of ultra-fast-triggered semiconductors, and how such devices can aid US national goals to develop future high-performance resilient power systems.

#### Renesas presents wireless power transmitter update

New wireless device charging technology improves efficiency, measurement accuracy and user safety

RENESAS ELECTRONICS presented advancements in its charging technology at the International Solid-State Circuits Conference (ISSCC) in San Francisco, February 19-23. During the conference, Renesas described its single-chip wireless power transmitter solution that measures AC and DC transmitter power for improved accuracy and safety.

The presentation also included details of a transmitter technology with adaptive Zero-Voltage Switching (ZVS) that achieves reduced electromagnetic interference (EMI) and higher power transmission efficiency. These technical capabilities enable wireless power transmission up to 15W with a Qi power receiver (PRx) and up to 40W with proprietary PRx solutions.

#### DC and AC Coil Current Sensing and Foreign Object Detection

Renesas is the first in the industry to develop single-chip transmitter (Tx) technology that can directly measure both DC and AC power transmission components. With this approach, transmitted power can be measured more accurately, providing a means to accurately detect a mismatch between the power transmitter (PTx) and the PRx power levels.

Furthermore, DC and AC coil current sensing can detect if a small metal foreign object, such as a paper clip, is caught between the transmitter and receiver, which otherwise could cause the object to heat up and compromise safety.

The transmitter is equipped with analogue AC coil current sensors and supports up to four transmitter coils to increase the charging area, improving the end user's charging experience.

#### Adaptive Zero-Voltage Switching and Low EMI

One of the key innovations to be described at the ISSCC presentation is adaptive ZVS, which ensures that the power MOSFETs switch after their drain-source voltage has dropped to 0V, reducing switching losses and increasing efficiency. Since this adaptive ZVS technology operates over wide load conditions, it is ideal for half-bridge inverters powering varying loads. Moreover, this ZVS technology reduces EMI by lowering the amount of energy that is converted into electromagnetic noise.

When compared to the conventional methods, using ZVS decreases EMI by 4 decibel (dB) and can increase the PTx efficiency by 1.7 percent or more. ZVS also helps extend the operational life of power systems in many applications such as automotive in-cabin chargers by auto-calibrating the initial threshold of the comparator. Additionally, the system has a highly programmable Pulse Width Modulation (PWM) generator, which controls the transmitter power delivery characteristics to ensure that the device being charged receives the right amount of power. This improves the accuracy and stability of the charging process and provides more control over the delivered power.

"With the integration of these innovative technologies, new wireless charging systems are expected to change the way portable devices are charged," said Filippo Neri, senior manager of Electrical Engineering for Renesas' Mobility Infrastructure and Industrial Power Division, who co-authored the paper."

#### Mitsubishi acquires Swedish DC circuit breaker firm

#### Scibreak and Mitsubishi to work together on DCCB tech for HVDC systems

MITSUBISHI ELECTRIC has entered into a share transfer agreement on February 16 to wholly acquire Scibreak AB, a Swedish-based company that develops direct current circuit breakers (DCCBs).

The two firms aim to work closely together on developing DCCB technologies for high- voltage direct current (HVDC) systems to support the increasing global deployment of renewable energy.

The introduction of renewable energy generation, such as wind power, is increasing worldwide to achieve carbon neutrality. Particularly in offshore wind power generation, HVDC is used for long-distance transmission between offshore and onshore load centres, as it offers lower power losses and cost when compared to AC transmission. In the future, multi-terminal HVDC

networks are expected to develop, particularly for offshore wind power generation in Europe, allowing for efficient cross-border energy transmission. These networks will require DCCBs, which will play a critical role in protecting the power system.

HVDC breakers will require very fast operation times, in the order of a few milliseconds, and companies are stepping up technological development in response to the need for more compact, high-performance, and cost effective DCCBs.

Scibreak has market leading DCCB technology, in terms of operation time and footprint. Through the acquisition of shares, Mitsubishi Electric says it will utilise Scibreak's technology and know-how to lead the market commercialisation of DCCBs.

➤ Pictured are Mitsubishi Electric Executive Officer Noriyuki Takazawa (left) and Scibreak CEO Tomas Modeer)

strengthening its global HVDC system business and contributing to the realisation of carbon neutrality through the further spread of renewable energy.

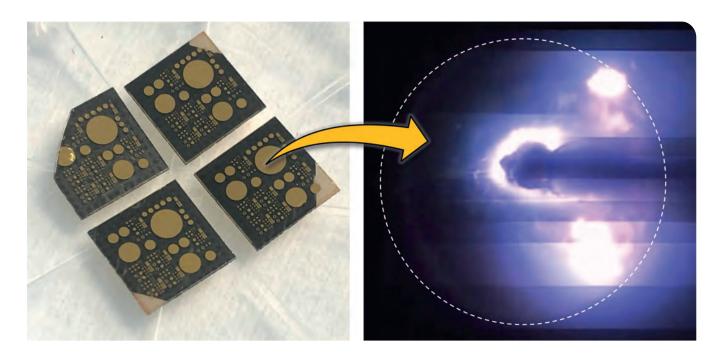

#### VisIC paves way to high-power GaN traction inverters

VisIC TECHNOLOGIES has successfully tested its  $2.2 m\Omega$  650V half-bridge power module, consisting of four parallel  $8 m\Omega$  Power FET, in a 3-phase configuration on a dyno-test-bench using a PMSM motor at a major automotive OEM.

The company say this proves its  $D^3GaN$  (Direct Drive D-Mode GaN) technology is well-suited even for the most challenging high-power automotive applications. Concerns about parallelisation and oscillations caused by fast-switching transients have been addressed. The inverter phase current reached 350Arms (500A peak) at 400V, although test system set-up limitations prevented higher currents, which the  $2.2m\Omega$  Power Module is capable of.

Worldwide Harmonised Light Vehicles Test Procedure (WLTP) driving cycle testing was executed and achieved comparable efficiency with commercial Silicon Carbide-based modules, despite using early non-optimised module prototypes. VisIC says this means that D³GaN will deliver its promise of the highest efficiency, improving car costs through lighter, smaller power systems and a smaller battery size, without compromising the car's driving range. In addition, the D³GaN technology, based on GaN-on-Silicon semiconductor process, is delivering better than SiC performance at the more competitive Silicon cost level.

"With this great accomplishment, acknowledged by a leading automotive OEM, VisIC Technologies has provided overwhelming evidence for higher-efficiency at lower-cost future EV traction inverters, for the automotive world," said Tamara Baksht, CEO &

co-founder of VisIC technologies. "The automotive market demands high-power, high-voltage, high-reliability GaN, and our D<sup>3</sup>GaN die and module solutions are the answer."

VisIC Technologies 3-phase prototype inverter system will be available for testing across additional customer sites towards the end of the 2nd quarter of 2023.

#### Microchip invests to expand SiC capacity

Ramping production in Colorado Springs fab will enable Microchip to respond to growing semiconductor demand

Microchip Technology has announced plans to invest \$880M to expand its SiC and silicon production capacity at its Colorado Springs manufacturing facility over the next several years. Microchip was also approved for state and local incentives of approximately \$47M for the expansion.

One significant phase of the expansion is to develop and upgrade its 50-acre, 580,000-square-foot Colorado Springs campus for increased SiC manufacturing for use in automotive/E-Mobility, grid infrastructure, green energy, and aerospace and defence applications.

The campus currently employs more than 850 people and produces products from 6-inch wafers. The manufacturing technology that Microchip is installing will run on 8-inch wafers, which will significantly increase

the number of chips produced at this location. The additional 400 jobs anticipated at the facility will range from production specialists to technical roles in equipment procurement and management, process control and test engineering.

"With over two-decades of investment in SiC, Microchip's portfolio is designed to provide our customers with innovative power solutions," said Rich Simoncic, senior vice president of Microchip's Analog businesses. "This campus is an integral part of producing our SiC technology to assure our customers with supply certainty as they transition to SiC solutions."

President and CEO of Microchip Technology Ganesh Moorthy said: "Microchip Colorado Springs has a long history of partnering with the city and state and we applaud their

continued support of our efforts to advance the semiconductor industry in the US. The CHIPS and Science Act is already making a positive impact on our business through the Investment Tax Credit and we are seeking capacity expansion grants for several of our semiconductor factories, including our Colorado Springs factory. We see a bright future in the region made possible by great partnerships, state and local incentives, and a strong local talented workforce."

#### Toshiba launches gate-driver for automotive DC motors

TOSHIBA has launched TB9083FTG, a gate-driver for automotive brushless DC motors used in applications such as electric power steering (EPS), electric brakes and shift-by-wire. Volume shipments start today.

The new product TB9083FTG controls and drives external N-channel power MOSFETs for driving a three-phase brushless DC motor. It is highly capable against the ISO 26262 2nd edition functional safety and supports ASIL-D for use in highly safety-critical automotive systems. This makes the new product ideal for automotive applications using brushless DC motors, such as EPS, electric brakes and shift-by-wire.

For systems requiring safety relays such as EPS, TB9083FTG has a built-

in three-channel gate-driver for the safety relays that control and drive the relays for motors and power supply. This eliminates the need for external components and helps reduce the part count.

TB9083FTG is housed in a P-VQFN48-0707-0.50-005 package with a wettable flank[4] structure. This allows visual inspection of solder joints using an automatic optical inspection (AOI) system, and contributes to improved solder joint reliability.

In addition, Toshiba has verified that it can go through 3000 cycles in the mounting temperature cycling test and has obtained data that will allow customers to use this QFN package with full confidence.

By using a small package ((7.0mm x 7.0mm (typ.)), the mounting area has been reduced by approximately 66 percent against the current product. This helps to control the increase in the mounting area, as the number of electronic components on ECU boards tends to rise due to redundant designs that are effective in ensuring higher levels of safety.

# **Connecting Semiconductors and Electronics**

#### SMART DATA-AI

WORKFORCE DEVELOPMENT

> **Global** ADVOCACY

> > Sustainability

1000+ STANDARDS

THOUGHT LEADERSHIP

#### **SEMICON**

TECH COMMUNITIES

**SEMI**UNIVERSITY

**Cyber** Security

#### About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

# Virtualisation: a key enabler of the future power grid

Power grids are undergoing a period of radical change. This feature explores the transition to virtualised protection and control in the age of renewables.

#### BY HENRY NIVERI, PRODUCT MANAGER AT ABB

POWER GRIDS are shifting away from an aging infrastructure designed for one-directional power flow to one able to integrate dynamic renewable energy resources.

To address this complex challenge, operators are looking for new solutions for sustainable power generation, responding to increasing demand and supply requirements whilst maintaining grid stability.

The virtualisation of protection and control forms a key part of this journey, offering new possibilities to optimize the supply of renewable generation and achieve flexibility and scale. The transition to virtualised protection and control is one of the enablers in the battle to stabilise the electricity grid in the age of renewables. The energy transition is certainly on. Already about 30 percent of the world's electricity comes from renewables, including hydropower, solar and wind. By 2026 this figure is forecast to rise to the equivalent of today's fossil fuel and nuclear energy capacity combined.

But while this emerging new energy economy may be critical to our low carbon future, integrating these new energy sources is having a fundamental impact on the electrical grid. Put simply, our aged grid infrastructure was not designed for the renewable energy revolution. It was only designed to deal with a steady, reliable supply of energy, under the basic assumption that electricity generation is easily adjustable depending on the amount of electricity consumed. The inherent variability of wind and solar, including potential imbalances in supply and demand and changes in transmission flow patterns, make load balancing on the existing grid problematic.

This becomes even more complex when considering the current rate of added distributed energy generation. Today, we are seeing customers taking a more active role in generation, as energy production has become more accessible for all. We have also seen a rise in microgrids being powered by the growth in solar and wind. More decentralized resources enable a more resilient system and allow small and large power consumers alike to produce much of the electricity they need locally. However, distribution system operators still need to ensure stability and alignment between generation and demand.

Add to the mix a changing grid profile, as electricity needs evolve with rapid electrification driven by electric mobility, heating and ventilation, data centers and emerging industries, and it becomes clear that the world needs innovative approaches to balance the grid – and fast. Enter virtualisation which is set to become a key enabler in efficient supply and demand management, optimization and, in turn, grid stability.

#### Virtualisation in electrical distribution

Virtualisation – which, in simple terms, means creating a virtual, rather than actual, version of something – can help to stabilize the electrical grid in several ways.

But to understand how, we must first look at a typical modern substation. Though the size of today's substations can be variable, typically those that serve the power generation sector can be the size of a football field, and house, at the most basic, circuit breakers and switches, isolators, transformers and a busbar system to enable the smooth functioning of transmission and distribution systems.

Though, as the power grid needs continue to evolve, today's substations are increasingly integrating additional technology too. From communication components, such as routers, Ethernet and mobile phone networks, and operator terminals through to SCADA (Supervisory Control and Data Acquisition) systems to enable full monitoring and control of all connected devices, most substations today have multiple computing devices, both legacy and newer assets, running specific applications and working in isolation.

This can make maintenance a minefield for the standard operator, tasked with keeping track of an ever-growing list of varied components. In most

cases too, because individual devices have vendorspecific properties, for example, communication interfaces or engineering tools. This means any modifications involve a specialist skillset to be outsourced at a cost. This requirement will continue to grow as more digital functionalities, such as increased monitoring, diagnostics and analytics, are added.

Further, more devices mean more space required in a substation, making the task of physically installing and maintaining each asset a challenge in itself. Additional considerations include the expenditure associated with power supply, cooling, heating and ventilation requirements, maintenance and whole lifecycle management. Through virtualisation, it becomes possible to address many of these challenges by consolidating multiple workloads, such as protection and control, from various pieces of equipment into one single, easy-to-use platform. In short, virtualisation separates software functionality from the physical device.

As the first major benefit, virtualisation drastically reduces the number and type of devices in substations. These devices could be handling, for example, protection, control, monitoring, diagnostics, and communication. This means that there are fewer devices to replace, test, commission and maintain. As there is only one kind of hardware running all the different tasks it effectively eliminates the need for users to learn the specifics for each device and reduces the amount of knowledge required to maintain the substation. It also enables most key activities to be performed remotely, in real-time, anywhere in the world, negating the need for a physical presence. The result is faster, less expensive operations.

But the benefits do not end there. What is equally appealing about virtualisation is the ability to aggregate all the data from various devices in the substation into one single location. For the utility provider, the wide-reaching visibility afforded by this approach can empower better decision making in power quality, renewable integration, asset management and more.

#### Virtualised protection and control

Inherently, the switch from a conventional approach to a virtual one will not happen overnight. As with all big innovation, it will only be achieved through incremental steps – the first of which will be the shift towards virtualised protection and control.

As many utility operators know, handling protection and control is complex, because of the involved engineering and maintenance required with interdependencies born out of the increasing amount of intelligent devices. Take, for example, the growing demand and the increasing penetration of large-scale intermittent sources, such as wind farms and solar panel systems, which place new pressures on the need to balance local supply and demand

#### RENEWABLE POWER

as much as possible, maintain voltage levels within tolerances, and control power quality and reliability at connection points.

Given the typical complex setup, which can entail any number of varying protection and control, measurement and communication devices which needed to be both physically installed and integrated into the established substation, the resulting system can be complex to maintain. This is where virtualisation comes in. By virtualising protection and control functions, it becomes possible to upgrade, maintain and operate the protection and control arrangement in real-time with ease.

Working via one central software platform also makes it easier to analyse and act upon the data obtained from the assets, individually and collectively. For the busy utility operator, this level of insight will be game-changing. Through a more holistic overview, it will allow energy distributors to respond to significant changes far better and even prepare for them ahead of time. This strategic approach also affords the ability to identify and address issues before they escalate and analyze recurring trends to anticipate similar failures or performance constraints. Virtualisation also entails less material requirements and curbs the carbon footprint associated with material manufacturing. Other benefits include simplified life cycle

**FURTHER READING**

- 1. https://www.iea.org/reports/global-energy-review-2020/ renewables

- ➤ 2. https://www.iea.org/news/renewable-electricity-growthis-accelerating-faster-than-ever-worldwide-supporting-theemergence-of-the-new-global-energy-economy

- 3. https://new.abb.com/news/detail/78658/abb-technologyenables-uk-grid-to-integrate-more-renewable-energy

management and flexibility to scale with ease.

A strong example of this is ABB working with UK Power Networks, as a part of the Constellation project<sup>3</sup>, to develop a wide area protection system that uses the 5G telecoms network for communication between substations. Based on the IEC 61850 standard, the system will enable real-time monitoring and control of distributed energy resources such as wind and solar farms.

With thousands of substations across Great Britain, UK Power Networks' new approach has the potential to unlock 1.4 gigawatts (GW) of network capacity that will enable further integration of DER. This would achieve annual savings of 19 million tons of CO<sub>2</sub> emissions and would be a significant step in the right direction for the UK to reach Net Zero by 2050. Constituting a complete industry first, this ground-breaking system follows in ABB's ongoing investment into the virtualisation of protection and control in recent years, with new further innovations in the pipeline.

#### An enabler for change

The world's energy mix is evolving at pace, and the reality is that utilities will still need to redesign, if not completely overhaul, the grid infrastructure to respond to the challenges that have arisen.

In the interim, sharper focus will be placed on those solutions which can support greater renewable integration and evolving power needs in the now. The virtualisation of physical assets will prove a critical tool, empowering utility operators with the advanced capabilities and intelligence needed to streamline operations, optimise processes and prepare for changes in grid behaviour ahead of time. Not only will this inevitable shift make for a more stable grid but also have a positive impact on the environment. Clearly then, the era of virtual protection and control has arrived.

WE meet @ embedded world

Hall 2-110

#### Noise free e-mobility

e-Mobility is no longer a question of tomorrow and the number of e-vehicles is increasing day by day. Handling EMI noise is becoming more and more crucial, when it comes to design new electronic devices and systems. Würth Elektronik offers a wide range of EMC components, which support the best possible EMI suppression for all kinds of e-mobility applications. With an outstanding design-in support, catalogue products ex stock and samples free of charge, the time to market can significantly be accelerated. Besides ferrites for assembly into cables or harnesses, Würth Elektronik offers many PCB mounted ferrites and common mode chokes as well as EMI shielding products.

www.we-online.com/emobility

#### Highlights

- Large portfolio of EMC components

- Design-in-support

- Samples free of charge

- Orders below MOQ

- Design kits with lifelong free refill

# Bidirectional GaN switches are disrupting power management

Bidirectional voltage blocking and current conduction is an important function in overvoltage protection. How can BiGaN devices help?

BY THOMAS ZHAO, DIRECTOR OF R&D; DAVID ZHOU, VP OF R&D; FELIX WANG, VP OF PRODUCT DEVELOPMENT; AND DR. JAN ŠONSKÝ, VP OF ENGINEERING AT INNOSCIENCE

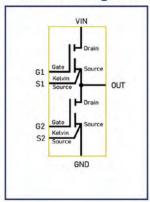

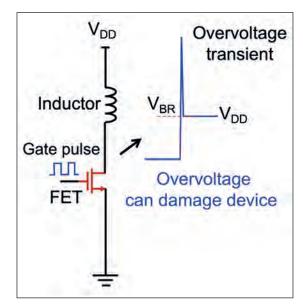

BIDIRECTIONAL voltage blocking and current conduction is an important function in overvoltage protection on USB ports, switching circuits for devices that operate from multiple power sources and high side load switches. But until now, designers have been limited to using two N type MOSFETs connected back-to-back in a common source configuration.

Such a solution requires two components and suffers from limitations related to on-resistance (RDS(on)), safe operating area (SOA) and other parameters. Innoscience's Bidirectional gallium-nitride (BiGaN) switch is a disruptive solution that reduces power dissipation and offers a significantly smaller footprint. This article introduces our innovative BiGaN device structure, reviews the performance of BiGaN devices and elaborates on different driver configurations for BiGaN.

The integration limitations with MOSFETs are mostly a result of their vertical structure that makes it extremely challenging to put two FETs onto one die with optimised cost, RDS(on), and voltage ratings for devices rated for about 30 V and above. The lateral structures of GaN HEMTs and the lack of a parasitic body diode makes it relatively easy to create a monolithic bidirectional GaN switch.

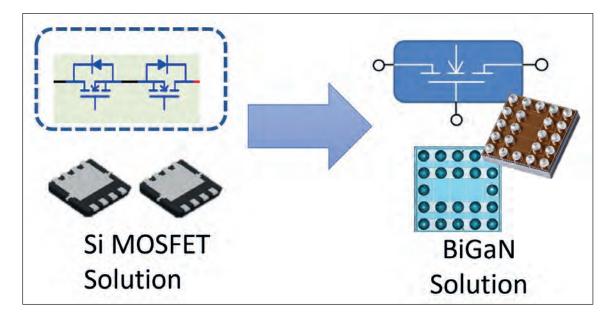

In a smartphone, for example, replacing back-toback MOSFETs with a BiGaN HEMT reduces on-state resistance by 50 percent, chip size by 70 percent, and temperature rise by 40 percent (Figure 1).

#### Losing the losses, shrinking the footprint

The adoption of an over-voltage protection (OVP) switch in the battery management system of a smartphone is driven by the desire to reduce total losses within the minimum possible footprint.

Figure 1.

Two back-to-back Si

MOSFETs are

replaced by

one BiGaN

In this particular use case, the power switch is either blocking voltage or conduction current without the need for frequent switching between these two states. Hence the switching losses determined by the gate charge are not important. The total losses are determined essentially only by conduction losses, and thus device total on-resistance.

Traditionally, the OVP functionality is realised by back-to-back discrete MOSFETs. Innoscience's solution is the BiGaN device, which is only slightly larger than a typical single GaN HEMT. It has significantly lower on resistance and is a smaller solution when compared to using two discrete devices in a bidirectional switch configuration.

For a conventional MOSFET, RDS(on) is the resistance between the drain and source when the device is fully on. The equivalent value of a BiGaN device is RDD(on) the resistance between the two drains when the device is fully on. For the 40 V INN040W048A BiGaN bidirectional switch with a drain current of 20 A, the max RDD(on) is only 4.8 m $\Omega$ , resulting in a very low conduction losses.

The package can be an important contributor to on-resistance. The lateral structure of BiGaN devices enables the use of a wafer level chip scale package (WLSCP) measuring only 2.1 x 2.1 x 0.54 mm INN040W048A. This package has minimal parasitic resistance, contributing to lower conduction losses and less thermal dissipation. The small package size also results in excellent on-resistance \* area performance (Ron\*A), an important factor in system miniaturization. And a single BiGaN device replaces two MOSFETs, further contributing to smaller solutions and a reduction in the bill of materials.

Overall, customers can make different trade-offs with Innoscience's BiGaN devices. One option is to maintain the existing space and footprint, while significantly reducing on-resistance and consequently also limiting temperature increase during charging. Alternatively, BiGaN by Innoscience

enables significant reduction in footprint for the OVP function, while keeping good on-resistance and thus efficiency.

#### SOA, Leakage and Robustness

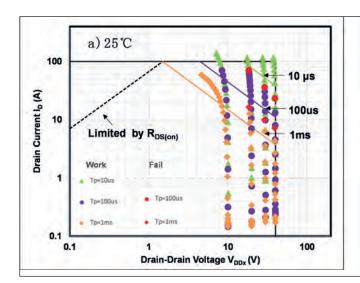

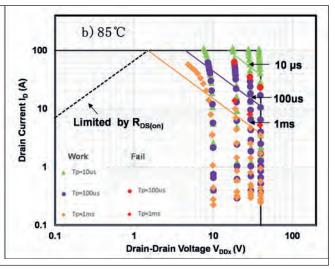

SOA is an important consideration for load switching applications. It's the combinations of voltage and current over which a device can be operated without damage or degraded performance. Factors limiting SOA include Ron, package considerations and thermal considerations. Improving the SOA of a Si MOSFET is challenging due to the negative temperature coefficient of the threshold voltage (Vth). Due to a reduced temperature dependence of VTH in GaN devices, BiGaN can maintain superior SOA performance also at high temperature (Figure 2).

Gate leakage is another important specification in bidirectional voltage blocking applications. Si MOSFETs have very good gate leakage performance. These devices have gate insulated from the channel by a gate oxideresulting in a sub- $\mu$ A leakage at 25 °C. Since Si MOSFET Vth

Figure 2: BiGaN INN040W048A SOA: a) 25°C; b) 85°C.

Figure 3: The inherent back-to-back diodes in the gate structure require that strict process control be implemented to achieve leakage under 3 μA at 85°C for BiGaN.

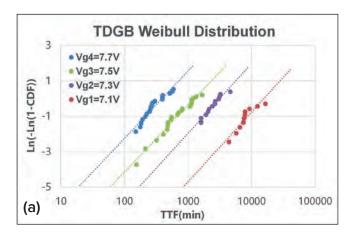

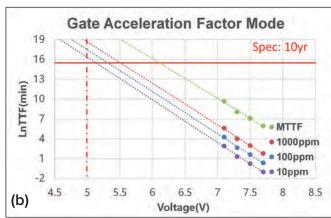

> Figure 4: BiGaN Gate robustness: a) TGDB Weibull distribution; b) Gate acceleration mode.

decreases at higher temperatures, the leakage current rises at elevated temperatures.

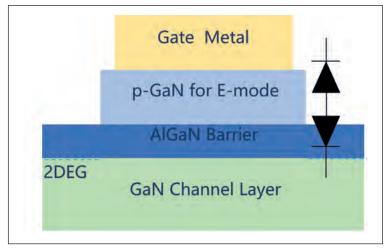

BiGaN devices have an inherently different gate structure that can be visualised as two back-to-back diodes (Figure 3). The upper diode is a Schottky structure with the gate metal as cathode and the pGaN as the anode.

The lower diode is a junction structure with a pGaN anode and an AlGaN cathode. Without proper control, the gate leakage of a BiGaN device would be higher than that of a Si MOSFET. Innoscience's R&D team has developed differentiating process steps and process controls to ensure the gate leakage is smaller than 3  $\mu$ A at 85 °C throughout the device lifetime. This was a critical requirement for its adoption in smartphone handsets.

Robust gate and drain operation are expected from all power switches. At 5.0 V (VGD) and 125 °C, the lifetime of BiGaN devices under continuous stress based on a 0.001 percent failure rate (10 ppm) exceeds 23 years. In actual applications, gate voltage spikes can be experienced from events such as short circuits.

The gate pulse capability of BiGaN devices is 10 million cycles at  $\le$ 8.5 V with a 1  $\mu$ s pulse width, at 25 °C and 85 °C, and 100,000 cycles at 9.5 V and

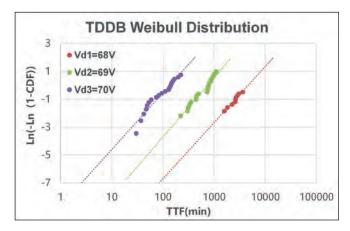

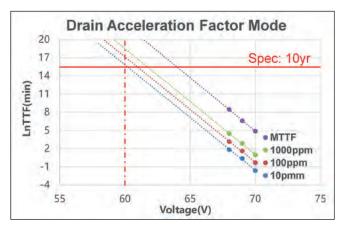

$85\,^{\circ}\text{C}$  (Figure 4). To measure drain robustness, INNO40W048A devices were exposed to continue stress of  $68\,\text{V},\,69\,\text{V}$  and  $70\,\text{V}$  at  $125\,^{\circ}\text{C}.$  The drain time dependent dielectric breakdown (TDDB) obeys the Weibull distribution and using the most conservative approach to

TDDB modelling, shows that at 32 V (VDD) and  $125\,^{\circ}$ C, the lifetime based on a 0.001 percent failure rate (10 ppm) for BiGaN exceeds 10,000 years (Figure 5).

#### **Driving BiGaN**

If the drive voltage is 5 V, existing drivers used with back-to-back Si MOSFETs can be used with BiGaN. In the case of smartphones, most charger ICs are compatible with GaN HEMTs with a 5 V gate drive. Drivers like the SC8571 from Southchip, NuVolta Tech's NU2205, switch capacitor drivers from Texas Instruments and power management ICs (PMICs) from Qualcomm are suited for driving BiGaN.

The gate voltage needs to be at least Vth (~1.7 V) above either Drain1 or Drain2 to turn on a BiGaN device. To turn it off, and block current flow in both directions, both gate to drain voltages (VGD1 and VGD2) need to be below Vth.

Pulling the gate to ground will turn off a BiGaN device. In 5 V applications, a charge pump can be

> Figure 5: BiGaN Drain robustness: a) TDDB Weibull distribution; b) Drain acceleration mode.

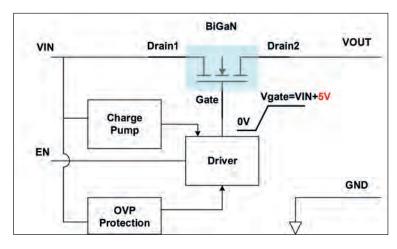

used to drive BiGaN (Figure 6). The gate voltage will be zero when EN is low and the BiGaN will be off. When EN is high, the gate voltage will be pumped to VIN + 5 V and the BiGaN will be ON and VOUT will equal VIN.

In applications other than smartphones, 5 V gate driver ICs are not commonly used. Those applications use drivers with a drive voltage of about 10 V designed for getting the lowest RDS(on) from Si MOSEETs.

Those drivers can't be used to directly drive GaN HEMTs since the drive voltage exceeds the gate's maximum rating. In these applications, a clamping circuit can be used where Zener diodes (D1 and D2) are used to clamp VGD at under 6 V (Figure 8). Diodes D4 and D5 have breakdown voltages over 40 V to provide drain-to-gate blocking.

#### Conclusion

The availability of high-performance, low-cost GaN-on-Si has enabled the development of BiGaN devices that can improve the operation of switching circuits for devices like smartphones that operate from multiple power sources, high side load switches, overvoltage protection on USB ports and similar applications.

As shown, BiGaN is reliable and easy to use. In smartphones, BiGaN can support fast charging with

➤ Figure 6: In 5 V applications, a charge pump can be used with a standard 5 V gate drive IC to turn BiGaN devices on and off.

lower temperature rises compared with solutions using back-to-back Si MOSFETs. In addition, the small solution size when using BiGaN enables the devices to be embedded in the handset, instead of the charger, to control battery charging and discharging currents.

Taking that function out of the charger can support smaller charger designs. BiGaN is a disruptive development that is enabling new design paradigms.

#### There is still life in the silicon IGBT

But silicon carbide is the long-term future for energy efficiency

Tesla's recent announcement that it will use 75 percent less silicon carbide (SiC) in a new powertrain for lower cost EVs sent a small shock-wave through the industry. With investment in SiC fabs running to billions of dollars from the likes of Wolfspeed, Infineon, STMicroelectronics, Onsemi, Microchip, and II-VI, surely SiC is the way forward for EV power electronics?

SiC MOSFETs offer faster switching and a higher temperature capability than silicon IGBTs, along with a smaller footprint for the passive components. All these factors make them ideal for EV drivetrain inverters. Except ... SiC chips are expensive. And until new fabs come on-stream, they will remain so. In this context, Tesla's plans to develop lower cost inverters based largely on silicon power devices makes sense, certainly in the short term. For similar reasons, silicon IGBTs will continue to make economic sense for many other power applications including wind turbines.

18 months ago when PGC, a consultancy dedicated to SiC technology, analysed SiC die costs, the retail price of 100A SiC MOSFETs (both 650V and 1200V)

was three times that of equivalent silicon IGBTs. The SiC die had the advantage, however, of taking up three to four times less space.

Earlier this year, Jelena Loncarski and Alberto Bellini from the University of Bologna and Hussain A. Hussain from Kuwait University, compared the efficiency, cost, and size of a SiC-based and an IGBT-based full-scale converter in a PMSG (permanent magnet synchronous generator) wind turbine. In this case, the cost of a SiC solution was twice as high as the silicon IGBT design.

The researchers' paper 'Efficiency, Cost, and Volume Comparison of SiC-Based and IGBT-Based Full-Scale Converter in PMSG Wind Turbine' in Electronics (2023), focused on a 2MW PMSG based wind conversion system with a bidirectional full-scale frequency converter comprised of two back-to-back inverters. Using a PLECS simulation tool, they compared wind energy systems both for the same switching frequency (low switching frequency suitable for IGBT modules) and also a SiC-MOSFET-based converter working at high switching frequencies.

They calculated that a SiC-based converter in the wind generation system would provide a similar efficiency to a silicon-based converter, but would reduce the system's size. In particular, the total volume of passive components was cut by 4.54 times (4.25 times in the case of 55 °C ambient temperature). However, as mentioned earlier, the price increase was a factor of two.

#### Power2Power

In 2019, 43 partners from industry and research (coordinated by Infineon in Dresden) began a three-year, EU-funded project called Power2Power to improve silicon IGBT technologies. The results suggest there's plenty of life left in IGBTs.

The project partners improved IGBT semiconductor manufacturing processes related to ion implantation, metallisation, device and yield optimisation. They also developed an advanced micro-pattern trench (MPT) IGBT that outperforms current approaches. And they enhanced pressure-less chip soldering, wire bonding, clip sintering and automated packaging.

For end applications, the project showed that IGBT-based energy conversion can reach an efficiency of over 98 percent for EV converters and drive trains. Moreover, IGBTs can cut the cost of rolling stock energy chargers by 30 percent and extend the lifetime of electric vehicle chargers by 1.5 times.

Jochen Koszescha, senior director of funding projects & coordination at Infineon, commented: "Even though new power semiconductor materials like SiC or GaN play an important role in supporting the efficient conversion to a sustainable, independent energy supply, silicon-based power semiconductors are predicted to dominate the market even beyond 2030."

Underlining this trend, Renesas Electronics is rolling out a new generation of IGBTs, the AE5 series, targeted firmly at EVs. By reducing inverter power losses, these IGBTs are said to improve power efficiency by up to 6 percent compared to Renesas' previous generation technology, allowing EVs to drive longer distances. The devices are initially being built on 200- and 300-mm wafers at the company's fab in Naka, Japan. Next year Renesas will ramp mass production on a new 300-mm power semiconductor line in Kofu.

#### The future

Of course, as SiC-MOSFET modules prices drop, the benefits of SiC-based systems will become

more marked. "In order to have overall system cost and volume savings with the SiC-MOSFET-based conversion system, the price of the SiC devices should be substantially lower, at least two times in order to have an equal cost to the Si-based system," write Loncarski and colleagues in their paper about wind turbines.

They conclude: "The cost function applied to the efficiency, volume, and cost with different weights (less for the efficiency and equal to the cost and volume) has shown that the SiC-MOSFET-based converter at 30 kHz has the best value, regardless of its higher cost, when compared to a Si-IGBT converter, as the benefits in the volume reduction were superior."

A new IDTechEx report 'Power Electronics for Electric Vehicles 2023-2033' highlights SiC technology's benefits in the context of the shift from 350-400V to 800V in EVs. 800V allows joule losses to be reduced and high voltage cabling to be downsized.

Combined with 1200V SiC MOSFETs, this typically leads to 5-10 percent efficiency gains, which can potentially downsize the expensive battery, save costs, or improve the vehicle's range, says IDTechEx.

SiC's electronic properties make it well suited for higher-voltage applications, where it can deliver superior performance at a more competitive cost. As high-volume SiC device manufacturers ramp up production, SiC will increasingly become cost competitive with silicon.

Nevertheless, silicon IGBTs have dominated the medium-to-high power device range for 20 years. And may well continue to for a while longer.

# Targeting the C-band with ultra-high-voltage HEMTs

GaN HEMTs with a minimal output capacitance and terminated harmonics deliver record-breaking powers and efficiencies

BY SEBASTIAN KRAUSE FROM THE FRAUNHOFER INSTITUTE FOR APPLIED SOLID STATE PHYSICS IAF DURING THE LAST DECADE, the GaN-on-SiC material system has established itself as the dominating semiconductor technology for delivering very high powers in the gigahertz range. Its more established rival, silicon-LDMOS, is more popular, and the cheaper choice for powering most systems in the VHF and lower UHF spectrum. However, this incumbent is even losing market share in that application space to GaN: this wide bandgap rival is renowned for its higher device efficiency, which trims operational expenses; and its higher power per die area that enables the design of smaller and lighter systems.

The enviable position that GaN holds in the high-power market is primarily due to its capability to maintain a high efficiency, even at high voltages and hence high-power levels. In contrast, LDMOS struggles to find a sweet spot that ensures a good efficiency, alongside a high-power density and high-frequency performance. So usually a trade-off has to be made in device design, favouring one attribute. Or, to put it another way, GaN has the stamina to go

the extra mile, in terms of its frequency range, while LDMOS is already running out of gas.

However, there's a need to understanding the underlying physical principles of these limitations, and pinpoint the critical device parameters that require careful tuning, in order to optimise GaN devices. Clearly, device scaling does not come for free.

Looking towards higher frequencies, the predominance of GaN is built on its capability to deliver very high powers and efficiencies. Yet, generally accepted scaling rules apply, implying that operation at higher frequencies must go hand-in-hand with a reduction in supply voltage. Consistent with this expectation are the product portfolios of manufacturers: they list the availability of 65 V devices up to 2 GHz, while those capable of 12 GHz and 18 GHz seem to mark the final frontier for 50 V and 40 V transistors, respectively. Beyond that, devices are rated for 28 V operation, if at all.

Last summer Integra Technologies of El Segundo, CA, launched a packaged 100 V GaN HEMT. This product pushes the boundaries for the supply voltage and ultimately the output-power-per-device. Designed for L-band avionics radar operating in the 1.030 GHz to 1.090 GHz band, this HEMT adheres to the mapped-out trend, highlighting once again that higher frequencies must be traded for supply voltage.

There are applications demanding kW-level powers higher in the spectrum, such as the C-band (4 GHz to 8 GHz) and even the X-band (8 GHz to 12 GHz). It makes much sense to try and address these opportunities with GaN, by taking on the challenge of marrying its high-frequency attributes with its outstanding high-power capabilities.

#### Keeping control of the charge

Unfortunately, when designers move to higher voltages, there is not much working in their favour. In fact, almost every critical performance parameter appears to get worse when raising the supply – there are problems associated with the transition frequency, greater trapping and diminished reliability to name but a few. All these issues stem from the rising electric field, which is the main factor to consider when trying to maintain performance when shifting operation to higher voltages.

Another major downside of a higher electric field is that it can lead to so-called 'short-channel effects'. When this happens the gate, which is solely responsible for controlling the electrons in the channel under ideal conditions, struggles to do its job. Short-channel effects tend to be associated with high-frequency technologies, because their occurrence usually leads to an 'under scaling' of electrical parameters – that is, electrical parameters scale less than what the scaling rules imply. Note that broadly speaking, scaling up in frequency or in

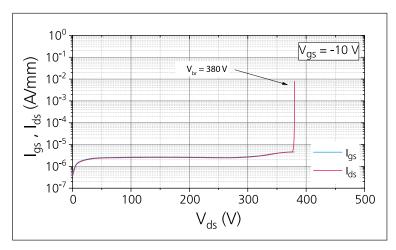

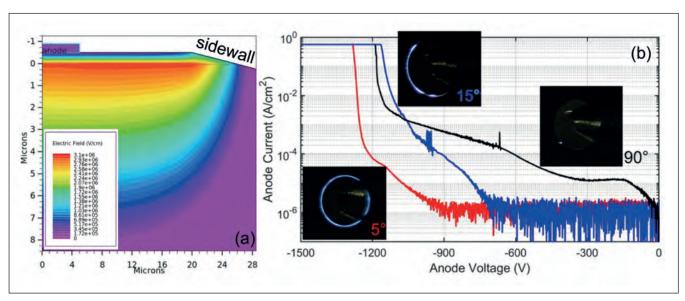

> Figure 1. Drain-Source breakdown characteristics for a device with a total gate width of 1.2 mm (6 x 200  $\mu$ m). For the measurement, the source of the device is grounded, whereas the gate potential is set to - 10 V. Then the drain potential is quickly raised until the recorded gate and drain current exceed the compliance value of 1 mA/mm, which is considered as breakdown.

voltage leads to similar field-related issues, unless appropriate countermeasures are taken.

One common countermeasure is to introduce field plates, a concept found in most GaN technologies up to Ka band. As its name suggests, the role of the field plate is to tame the electrical field by spreading this out from the gate towards the drain electrode. With its addition, there is a reduction in the maximum electric field close to the gate contact, and a quashing of short-channel effects. Another benefit is that a device can realise a higher breakdown voltage for a given on-resistance. Since a higher on-resistance translates to increased losses, it is crucial to keep this as low as possible when targeting the highest efficiency.

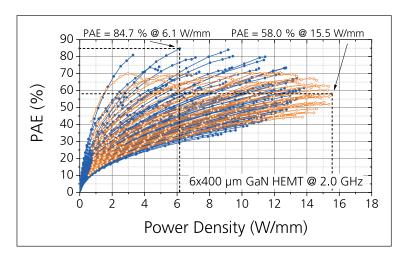

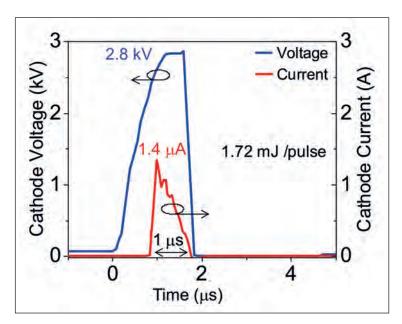

> Figure 2. Pulsed load-pull measurements of a 100 V GaN HEMT with a total gate width of 2.4 mm (6 x 400  $\mu$ m) at 2.0 GHz. The pulse width is 100  $\mu$ s with a duty cycle of 10 percent. Two conditions are plotted here. Orange is for load pull at the fundamental frequency without termination of harmonics, while blue is for fundamental load pull with second harmonic impedances at input and output set for maximum efficiency.

#### TECHNOLOGY | RF ELECTRONICS

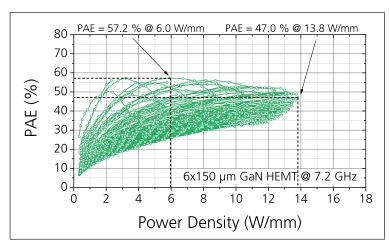

> Figure 3. Pulsed load-pull measurements of a 100 V GaN HEMT with a total gate width of 0.9 mm (6x150  $\mu m$ ) at 7.2 GHz. The pulse width is 100  $\mu s$ , with a duty cycle of 10 percent. No harmonics have been terminated during the measurement.

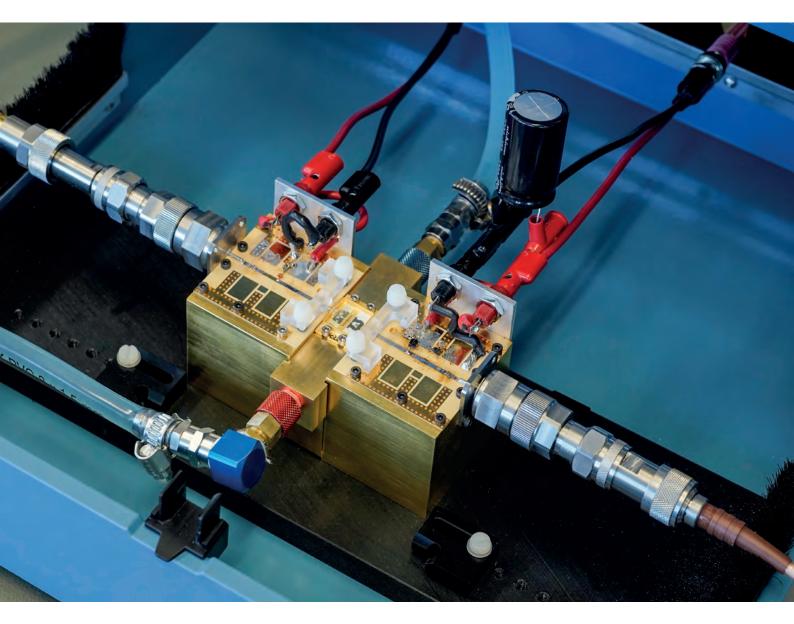

Working at the Fraunhofer Institute for Applied Solid State Physics IAF, our team is engineering devices to try and meet these criteria. Measurements show that the breakdown voltage for our 100 V GaN HEMTs is in excess of 350 V (see Figure 1). Meanwhile, on-resistance is just 4.2  $\Omega$  mm, a value merely one-third higher than that of established 50 V GaN processes.

#### Setting the stage for harmonics

At first glance, it would appear to be rather conservative to have such a high breakdown voltage for a 100 V device. However, there is good reason behind this caution – harmonic termination. When you dive a bit deeper into high-efficiency amplifier design, you are very likely to come across this technique of manipulating harmonic impedances.

Ultimately limiting the efficiency of an ideal amplifier is its class of operation. While class A and class B are probably familiar to most of us, brave designers opt for class E, class F or class F-1, which is also known as inverse class F. These latter three have a theoretical efficiency of 100 percent, while class B and class A are limited to 78.5 percent and 50 percent, respectively. In practice, all these numbers are impossible to achieve, due to the lossy nature of real devices. However, efficiencies as high

as 90 percent have been demonstrated for GaN HEMTs. I doubt you expected a free lunch, so you'll not be surprised that harmonic termination comes at a cost. Presenting specific impedances to the device at its harmonic frequencies – ideally a short or open circuit – alters the time domain waveform at the device output. For Class E and class F¹, there can be waveforms with a voltage magnitude as high as three-and-a-half times the supply voltage. Such a high voltage arises due to the high second harmonic impedance (at or close to an open circuit) that is required for the operation modes. Due to this, a sufficiently high breakdown voltage is a prerequisite for reaching the highest efficiency levels.

At higher frequencies the concept of harmonic termination slowly falls apart. This arises because real devices show a finite output capacitance in parallel to the intrinsic current source. Over frequency the reactance of the output capacitance decreases, forming a shunt current path to ground. If the designer now tries to force the device into class-E or class-F-1 operation, the open circuit at the second harmonic is bypassed by the output capacitance. At a certain frequency this results in an effective short-circuit for the second harmonic and all higher harmonics. This set of shorted harmonic impedances leads to the class-B condition, limiting the maximum theoretical efficiency from 100 percent to 78.5 percent.

In addition to this road block to realizing a high efficiency at high frequencies, there is another issue associated with high voltages. In this case it is the praised field plates that are part of the problem. Most troublesome are the so-called sourceterminated field plates – they can account for a large proportion of a device's output capacitance. It's tempting to simply ban this form of field plate from the device layout, but such a move would contradict the goal of proper field control. Like many times in life, it's better to seek a good trade off.

#### Stepping up in efficiency

Previously, we demonstrated a power-added efficiency of more than 77 percent at 1.0 GHz, a record for 100 V GaN HEMTs at the time. However, we uncovered some weak spots when we compared this device to our baseline 50 V devices. Deficiencies included a maximum efficiency that lagged the baseline devices by around 7 percentage

We believe that more is possible. There is no reason to think that the C-band is the ultimate limit for 100 V GaN HEMTs. Our high levels of performance at these frequencies imply that there is still room to push the technology towards the X-band.

# "POWER AHEAD" IN THIN FILM PROCESSES ON Si, SiC & GaN

Choosing Evatec's CLUSTERLINE® family of 200 or 300mm tools is a sure way to "power ahead" of the competition. From Frontside processes like trench filling, wetting, barrier, or capping layers, to backside etch and metallization processes for contacts, our thin film process know-how on Silicon and WBG materials ensures the best device performance while our wafer handling and stress management for thin wafers delivers the best production yields.

Visit evatecnet.com/markets/power-devices to find out how you can power ahead in your own production or contact your local Evatec Office at evatecnet.com/about-us/sales-service

#### TECHNOLOGY | RF ELECTRONICS

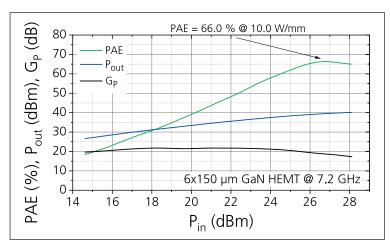

> Figure 4. Pulsed load-pull measurements of a 100 V GaN HEMT with a total gate width of 0.9 mm (6 x 150  $\mu m$ ) at 7.2 GHz. The pulse width is 100  $\mu s$ , with a duty cycle of 10 percent. For this measurement a 'trade-off' of fundamental impedance was chosen that yielded a good combination of efficiency and power density. Additionally, the second harmonic at the output of the device was set for the value that showed the highest power-added efficiency.

points. We also observed a pronounced efficiency roll off when measuring our 100 V devices at higher frequencies.

To address these weaknesses, we decided to make a fresh start. This involved redesigning the epitaxial stack and the intrinsic device features, with the goal of tightening the electrostatics. When we extracted the drain-induced barrier lowering – a measure that quantifies the parasitic control over the electrons by the drain contact, with the lower the value the better – we verified our success. This key figure of merit showed a five-fold reduction, yielding a value below 1 mV/V. In a nutshell, this result reveals that the gate has all the power over the electrons, without any interference from the drain at high voltages.

Further measurements underscored the capability of this new device. They revealed a record-breaking power-added efficiency for our 100 V GaN HEMT at 2.0 GHz of 84.7 percent – that's an increase of almost 8 percentage points, despite a doubling in frequency. The maximum power density hit 15.5 W/mm (see Figure 2).

#### **FURTHER READING**

- S. Krause et al. "100-V GaN HEMT Technology with Record-High Efficiency at C-Band Frequencies," International Conference on Compound Semiconductor Manufacturing Technology (CS MANTECH), Monterey, CA, USA, 2022

- S. Krause et al. "High-Power-Density AlGaN/GaN Technology for 100-V Operation at L-Band Frequencies," 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 17.4.1-17.4.4

There's more to our second-generation device than just headline-grabbing figures. By revising the intrinsic device layout, we have shaved off as much of the output capacitance as possible without deteriorating electrostatics. This refinement should enable these transistors to operate efficiently at much higher frequencies than before. By trimming the output capacitance by 40 percent, theory would suggest that these devices are susceptible to harmonic termination at higher frequencies.

Evidence from the lab supports this view. Measurements at the upper C-band frequency of 7.2 GHz – used by the European Space Agency for Deep Space Antennas to track spacecraft throughout the complete solar system – provide very impressive results. According to fundamental load-pull measurements, the power density is only a little down from the value for 2.0 GHz, reaching an impressive 13.8 W/mm. Meanwhile, power-added efficiency tops out at 57.2 percent.

Still, the question remained on whether terminating harmonic impedances would enhance efficiency. Due to set-up limitations, we could not tune the input and output simultaneously, as we had done for the 2.0 GHz measurement. So we tuned just the output second harmonic, and selected a fundamental load that provided a judicious combination of efficiency and power density. We then optimized the second harmonic phase, until we found the setting that yielded the maximum efficiency (see Figure 4 for the results of the power sweep).

The reduction in the output capacitance has paid off. The power-added efficiency has climbed to 66.0 percent, an increase of around 9 percentage points compared with the load pull without second harmonic termination. This value also sets a new benchmark for the efficiency of 100 V GaN HEMTs in the C-band. No less impressive are the associated power density of 10 W/mm and the gain of 18.5 dB, both achieved at the maximum power-added efficiency.

Crucially, these performance numbers are realized simultaneously, rather than marking the individually best obtainable values – that sets these 100 V devices apart from commercially available GaN technologies. While the power-added efficiency of our ground-breaking HEMTs is comparable to the best 40 V and 50 V technologies, the power density and gain of our 100 V devices is a big step up from the capabilities of today's commercially available GaN HEMTs.

We believe that more is possible. There is no reason to think that the C-band is the ultimate limit for 100 V GaN HEMTs. Our high levels of performance at these frequencies imply that there is still room to push the technology towards the X-band. We don't know where exactly the frequency limitations of these high-voltage devices are, but we are prepared and willing to find out.

### **NEXT-GENERATION OPTICAL LITHOGRAPHY**

EVG®150 Resist Processing System

- Automated spin / spray coating and development processes in a new, fully modular, smaller footprint platform.

- Outstanding throughput for HVM processes using a high-speed, high-accuracy robot and advanced scheduler algorithms.

- Guarantees highly uniform coats ranging from demanding thick resist applications down to sub-micron layers.

# Controlling threshold voltage instabilities in SiC MOSFETs

System designers can now benefit from new test and stress procedures for SiC MOSFETs that realistically determine their worst-case threshold voltage variations

#### BY THOMAS AICHINGER FROM INFINEON TECHNOLOGIES

ONE OF THE GREATEST strengths of the SiC power MOSFET over its silicon-based equivalent is its capability to operate at much higher switching frequencies and lower losses. Thanks to this, engineers can build advanced power electronic circuits that feature smaller cooling units and smaller passive components. These gains are so highly valued that as well as opening up new applications, they are enabling SiC MOSFETs to replace silicon counterparts in existing applications, where new ground is being broken for lighter, more efficient system design.

When engineers design circuits with SiC components, they expect that as well as exploiting the performance benefits, they will not be held back by any compromise in quality compared with silicon counterparts. There is an expectation from these engineers of a predictable electrical parameter stability over lifetime.

Unfortunately, until fairly recently the initial general impressions of these engineers had been that SiC technologies are not quite there. There were concerns, for instance, regarding so-far-unknown threshold voltage ( $V_{\text{TH}}$ ) peculiarities, and their extraordinary electrical parameter drifts during reliability investigations. Scientific papers had shown large  $V_{\text{TH}}$  variations within short periods of stress, raising concerns that critical electrical parameters of SiC MOSFETs were highly variable, threatening to get out of control during operation in the field, sooner or later.

Until recently, the origin and the application relevance of these short-term  $V_{\text{TH}}$  instabilities in SiC MOSFETs had not been fully understood, with literature reporting a wide range of parameter variations. Various possible reasons have been proposed. One is that first-generation products had varied levels of quality; and a second is that fundamental issues hampered stable, reproducible measurements of crucial electrical parameters, such as the threshold voltage.

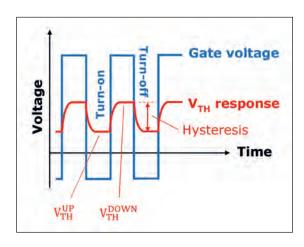

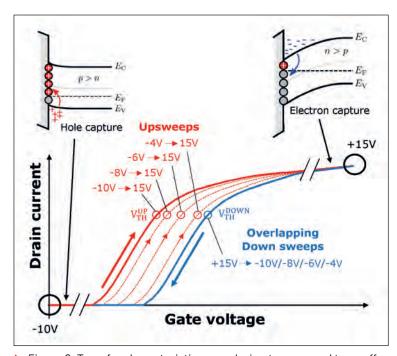

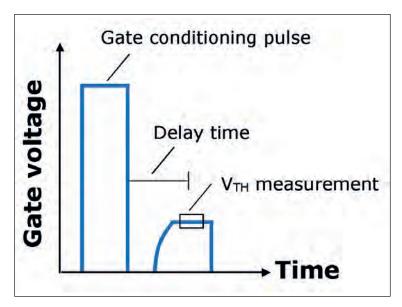

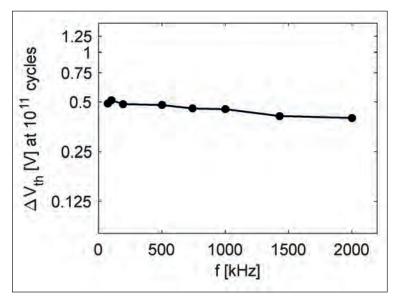

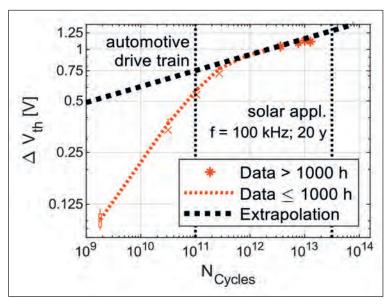

Recently, this second issue has been addressed by the release of new measurement guidelines for evaluating the  $V_{\rm TH}$  in SiC MOSFETs, published by JEDEC and drawing on contributions from our team at Infineon. We have gone on

to develop a deeper understanding of the trapping dynamics at the metal-oxide semiconductor (MOS) interface. Outlined in this first section of this article, this insight has helped us to adapt V<sub>TH</sub> measurement routines so that they resolve the issue of undefined and non-reproducible measurements.